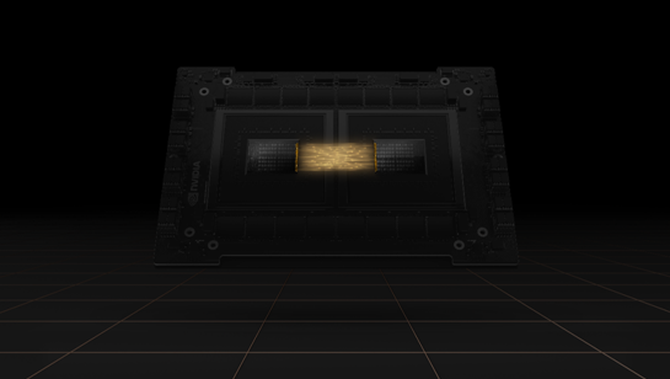

近日,NVIDIA宣布推出NVIDIA NVLink-C2C,这是一种超快速的芯片到芯片、裸片到裸片的互连技术,将支持定制裸片与NVIDIA GPU、CPU、DPU、NIC 和 SOC 之间实现一致的互连,助力数据中心打造新一代的系统级集成。

借助先进的封装技术,NVIDIA NVLink-C2C 互连链路的能效最多可比 NVIDIA 芯片上的 PCIe Gen 5 高出 25 倍,面积效率高出 90 倍,可实现每秒 900 GB 乃至更高的一致互联带宽。

NVIDIA 超大规模计算副总裁 Ian Buck 表示:“为应对摩尔定律发展趋缓的局面,必须开发小芯片和异构计算。我们利用 NVIDIA 在高速互连方面世界一流的专业知识,开发出统一、开放的技术,这将有助于我们的 GPU、DPU、NIC、CPU 和 SoC 通过小芯片构建出新型的集成产品。”

今日发布的NVIDIA Grace 超级芯片系列以及去年发布的 Grace Hopper 超级芯片均采用了NVIDIA NVLink-C2C 技术来连接处理器芯片。NVLink-C2C 现已为半定制芯片开放,支持其与 NVIDIA 技术的集成。

NVIDIA NVLink-C2C 支持 Arm AMBA一致性集线器接口(AMBA CHI)协议。NVIDIA 和 Arm 正在密切合作,以强化 AMBA CHI来支持与其他互连处理器完全一致且安全的加速器。

Arm 高级副总裁兼基础设施业务总经理 Chris Bergey表示:"由于未来的 CPU 在不断增加加速芯片和多芯片的设计,因此在整体生态系统中支持基于芯片的 SoC 至关重要。Arm 正致力于支持一系列广泛的连接标准,并使我们的 AMBA CHI 协议能够支持这些未来技术,包括与 NVIDIA 在NVLink-C2C上合作,以解决 CPU、GPU 和 DPU 之间的一致性连接等用例。"

NVIDIA NVLink-C2C 依托于 NVIDIA 世界一流的 SERDES 和 LINK 设计技术,可从 PCB 级集成和多芯片模组扩展到硅插入器和晶圆级连接。这可提供极高的带宽,同时优化能效和裸片面积效率。

除 NVLink-C2C 之外,NVIDIA 还将支持本月早些时候发布的UCIe(Universal Chiplet Interconnect Express,通用小芯片互连传输通道)标准。与 NVIDIA 芯片的定制芯片集成既可以使用UCIe标准,也可以使用 NVLink-C2C,后者经过优化,延迟更低、带宽更高、能效更高。

NVLink-C2C 的一些关键特性包括:

● 高带宽——支持处理器和加速器之间的高带宽一致性数据传输

● 低延迟——支持处理器和加速器之间的原子操作,对共享数据进行快速同步和高频率更新

● 低功耗和高密度——采用先进的封装,与 NVIDIA 芯片上的 PCIe Gen 5 相比,能源效率提高 25 倍,面积效率提高 90 倍

● 工业标准支持——支持 Arm AMBA CHI 或 CXL 工业标准协议,实现设备间的互操作性