从奔4到至强E5 英特尔处理器制程演变史

1/11

图解Tick-Tock战略之制程架构

2/11

在四十多年以来,摩尔定律的诞生一方面预测了英特尔和技术产业持续的以无法想象的方式进步,另一方面也鞭策着英特尔的发展。摩尔法则不是一个法则,而是一个机会。今天,要让芯片符合摩尔定律的发展显得越来越困难,成本越来越高,两个方面的因素制约着发展:由于半导体晶体管尺寸已经到几个纳米,再精细的工艺将会达到物理极限,而另一方,芯片厂投资的规模达到数十亿美元,极其昂贵,要保持摩尔定律的进步,要在基础科学和生产力上更大的突破。

3/11

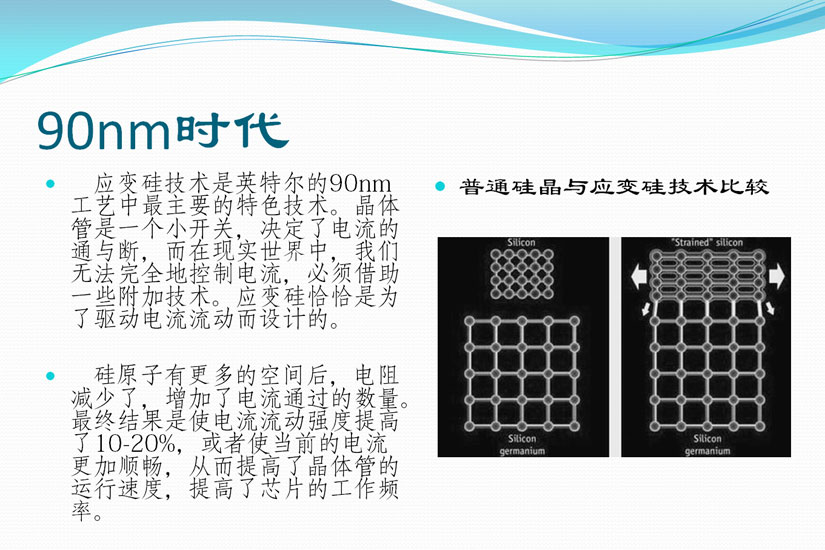

应变硅技术是英特尔的90nm工艺中最主要的特色技术。晶体管是一个小开关,决定了电流的通与断,而在现实世界中,我们无法完全地控制电流,必须借助一些附加技术。应变硅恰恰是为了驱动电流流动而设计的。

4/11

早在1985年IBM公司就已计划研发用铜替代铝作为芯片上的金属互连材料,但是直到1998年才在诺发公司(Novellus System)的帮助下把该技术应用在实际的集成电路制造工艺中。1999年苹果公司在400 MHz微处理器中采用了铜互连工艺,极大地提升了图形处理能力。

5/11

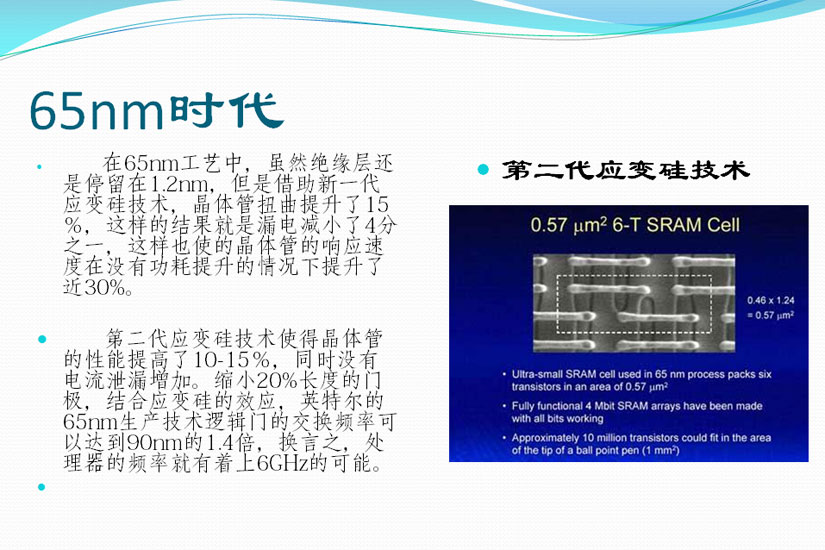

在65nm工艺中,虽然绝缘层还是停留在1.2nm,但是借助新一代应变硅技术,晶体管扭曲提升了15%,这样的结果就是漏电减小了4分之一,这样也使的晶体管的响应速度在没有功耗提升的情况下提升了近30%。

6/11

为了进一步降低漏电流,英特尔也在65nm中导入了NMOS Sleep Transistor技术,英特尔将其应用在动态关闭SRAM所用不到的区块,达成降低三倍漏电流的效果。与90纳米技术生产的晶体管相比,65纳米技术在同样的性能情况下可以使电流泄漏减低4倍。这样的话,65纳米技术生产的处理器在没有增加电流泄漏的情况下,提高了性能。

7/11

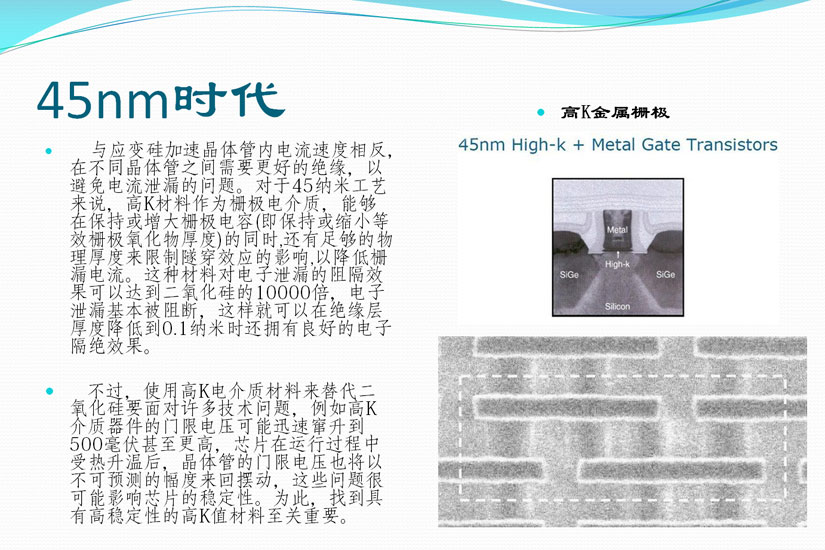

与应变硅加速晶体管内电流速度相反,在不同晶体管之间需要更好的绝缘,以避免电流泄漏的问题。对于45纳米工艺来说,高K材料作为栅极电介质,能够在保持或增大栅极电容(即保持或缩小等效栅极氧化物厚度)的同时,还有足够的物理厚度来限制隧穿效应的影响,以降低栅漏电流。这种材料对电子泄漏的阻隔效果可以达到二氧化硅的10000倍,电子泄漏基本被阻断,这样就可以在绝缘层厚度降低到0.1纳米时还拥有良好的电子隔绝效果。

8/11

在45纳米工艺引入的时候,第一次采用了“铪(Hafnium)”作为High-K栅极介质的基础物质,取代了沿用40年的二氧化硅,大幅度降低漏电率,同时栅极也采用金属栅极取代了以往的多晶硅栅极,所以总体来看,也就称为High-k + Metal Gate(HK+MG)。当然详细的金属栅极的材料信息仍属机密,我们无法知道太多,只知道它具有非常高的导电率。总体来说,铪和金属栅极的引入不愧为40年来最重要的一次变革。

9/11

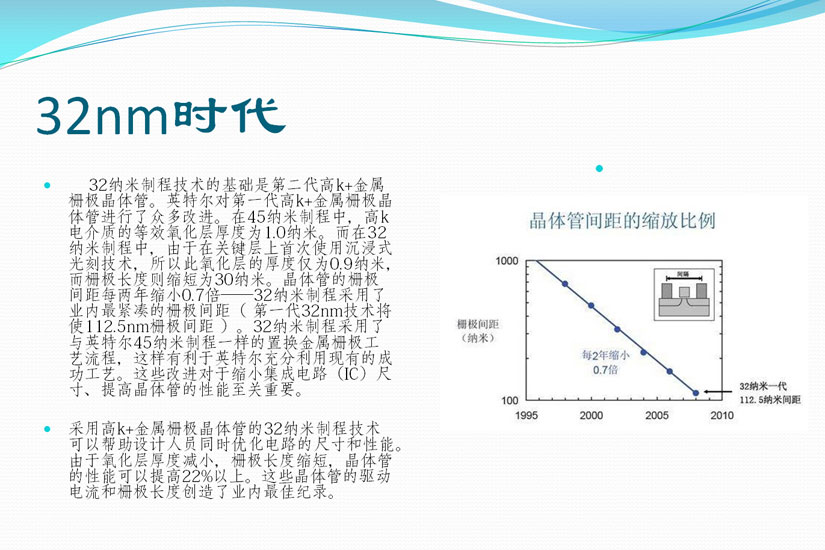

32纳米制程技术的基础是第二代高k+金属栅极晶体管。英特尔对第一代高k+金属栅极晶体管进行了众多改进。在45纳米制程中,高k电介质的等效氧化层厚度为1.0纳米。而在32纳米制程中,由于在关键层上首次使用沉浸式光刻技术,所以此氧化层的厚度仅为0.9纳米,而栅极长度则缩短为30纳米。晶体管的栅极间距每两年缩小0.7倍——32纳米制程采用了业内最紧凑的栅极间距( 第一代32nm技术将使112.5nm栅极间距 )。32纳米制程采用了与英特尔45纳米制程一样的置换金属栅极工艺流程,这样有利于英特尔充分利用现有的成功工艺。这些改进对于缩小集成电路(IC)尺寸、提高晶体管的性能至关重要。

10/11

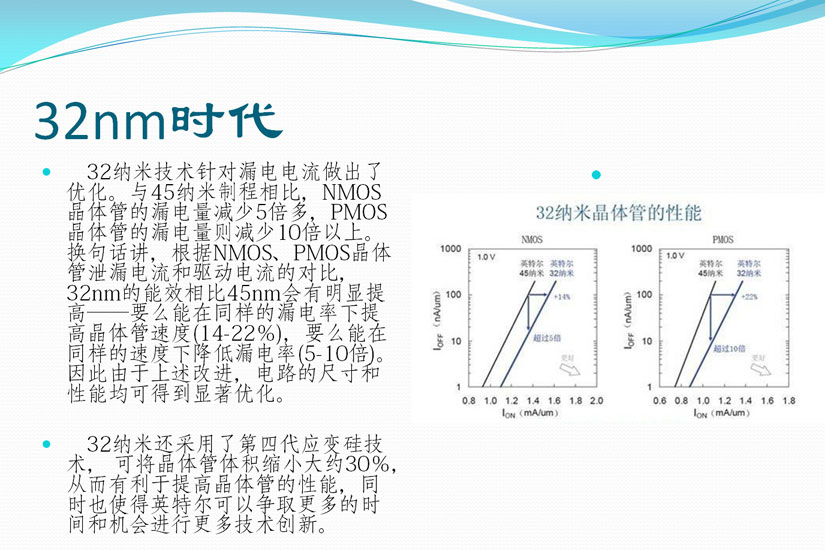

32纳米技术针对漏电电流做出了优化。与45纳米制程相比,NMOS晶体管的漏电量减少5倍多,PMOS晶体管的漏电量则减少10倍以上。换句话讲,根据NMOS、PMOS晶体管泄漏电流和驱动电流的对比,32nm的能效相比45nm会有明显提高──要么能在同样的漏电率下提高晶体管速度(14-22%),要么能在同样的速度下降低漏电率(5-10倍)。因此由于上述改进,电路的尺寸和性能均可得到显著优化。

11/11

当晶体管的体积原来越小,新的问题出现了——在应变硅、高K金属栅极都已经完成自己的使命之后,晶体管的漏电问题已经越来越严重,已经超出了功耗允许的范围。于是,3D晶体管技术出现了,3D Tri-Gate晶体管架构能够有效提高单位面积内的晶体管数量。3D Tri-Gate使用一个薄得不可思议的三维硅鳍片取代了传统二维晶体管上的平面栅极,形象地说就是从硅基底上站了起来。硅鳍片的三个面都安排了一个栅极,其中两侧各一个、顶面一个,用于辅助电流控制,而2-D二维晶体管只在顶部有一个。由于这些硅鳍片都是垂直的,晶体管可以更加紧密地靠在一起,从而大大提高晶体管密度。