【IT168 技术】Haswell处理器虽然已经发布了半年多,架构方面的很多细节也都早已公开,但是在内核尺寸、晶体管规模、功能模块分布、封装设计、Crystalwell eDRAM嵌入式缓存等方面,外界仍然所知甚少。在本周的ISSCC 2014国际固态电路会议上,Intel终于慷慨地放出了大量技术文档,揭开了Haswell底层的诸多秘密。

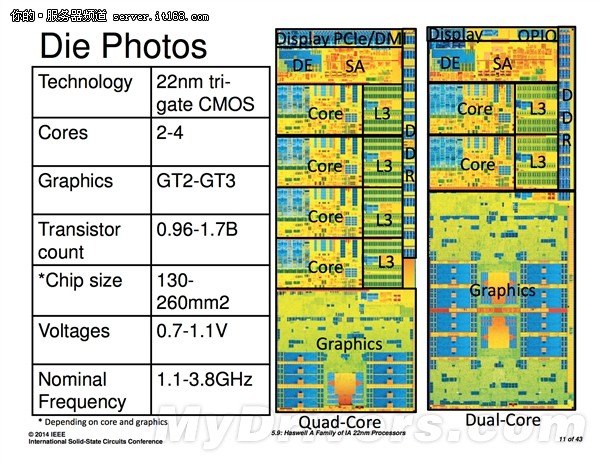

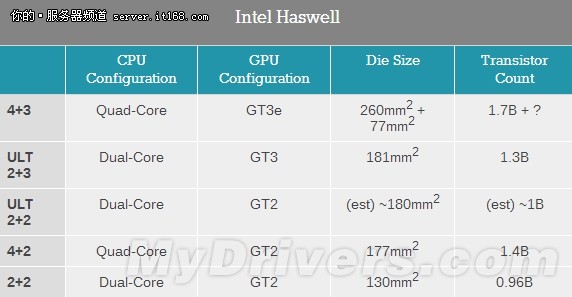

首先是不同版本的官方晶体管数量、内核面积。发布时,Intel仅公布了ULT 2+3(双核/整合芯片组/GT3核显)、4+2(四核/无芯片组/GT2核显)的数据,现在又给出了最大和最小的两个版本,基本齐了:

Haswell家族中最大个儿的当属四核心、GT3e核显加缓存。此前的粗略测量值为处理器264平方毫米、缓存84平方毫米,官方数据则是260、77平方毫米。处理器本身集成了大约17亿个晶体管,但缓存用了多少仍然是个谜。

最小巧的是双核心、GT2,仅仅130平方毫米,消耗了9.6亿个晶体管。

ULT 2+2(双核心/GT2核显)还是隐藏状态,但是简单计算可知,GT3、GT2两种核显之间差大约3亿个晶体管,因此ULT 2+2的规模差不多应该也是1亿个左右。

▲Haswell内核参数、四核GT2与双核GT3内核图

▲Haswell五种版本配置、内核面积、晶体管数量

▲Haswell五种版本的内部模块分布图

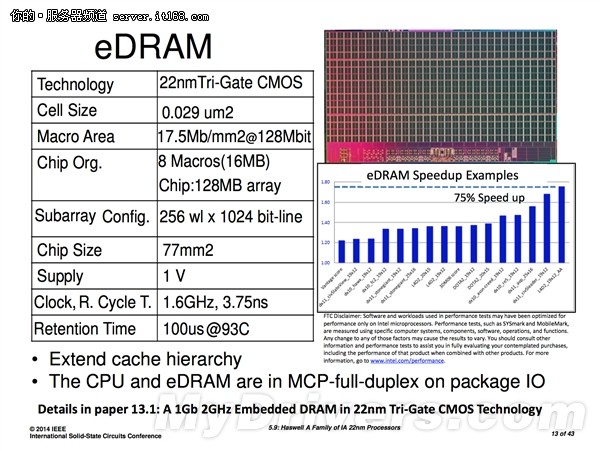

接下来说说缓存。同样是22nm 3D工艺制造,每个单元面积0.029平方微米,每平方毫米容量17.5Mb,总容量128MB,分为八个宏(Macro),每个16MB,运行频率1.6GHz。

Intel宣称,这些缓存可以带来10-75%的性能提升。

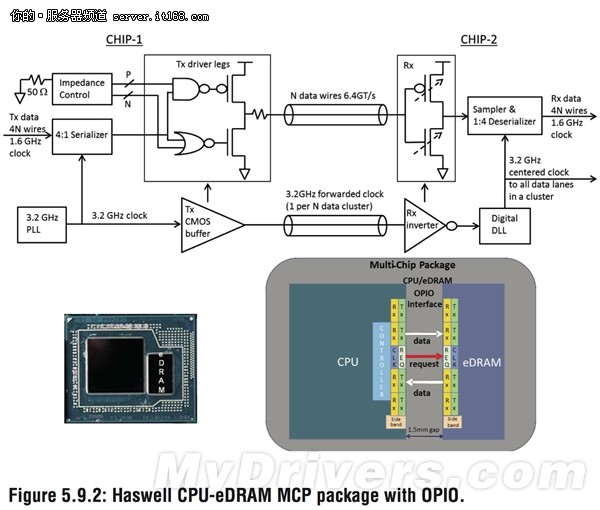

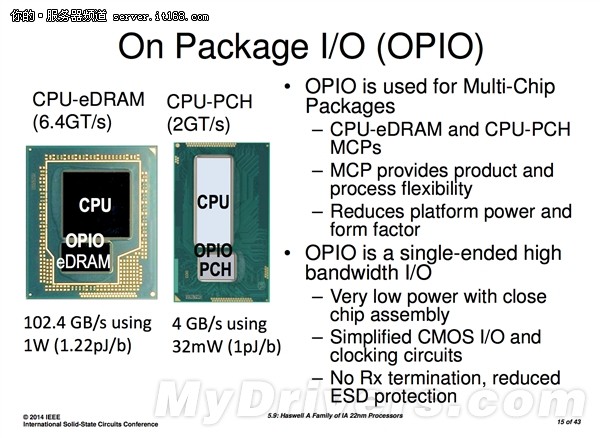

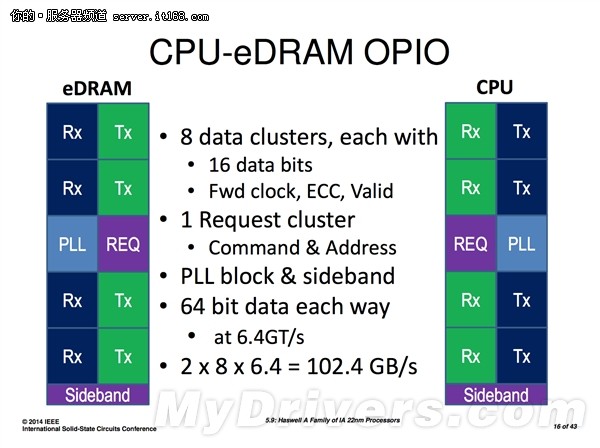

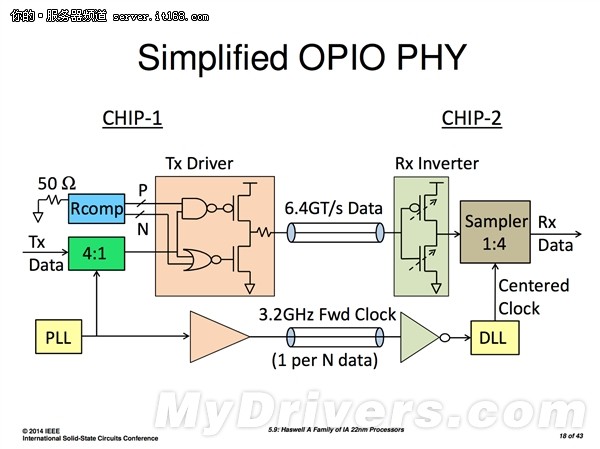

在处理器与缓存、处理器与整合芯片组之间,Intel都采用了所谓的OPIO(On-Package IO/整合封装输入输出)互连接口,位宽4×16-bit,其中与缓存之间速率6.4GT/s、带宽102.4GB/s、功耗1W,而与整合芯片组之间速率2GT/s、带宽4GB/s、功耗32mW。

处理器与缓存、芯片组之间的距离仅仅1.5毫米,OPIO因此可以做得极其简单,而且能够让产品和工艺更加灵活,并降低平台功耗和尺寸。

▲eDRAM缓存内核图、关键参数、性能提升

▲双芯片封装与互连架构

▲OPIO接口

▲处理器与缓存之间的OPIO

▲OPIO走线布局

▲OPIO PHY物理层

第三个方面是关于功耗优化的。

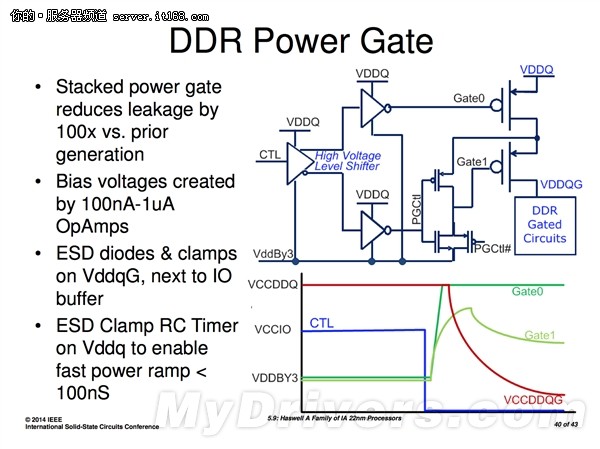

内存界面使用了新的堆栈式电源栅极,漏电率只有上一代的百分之一。

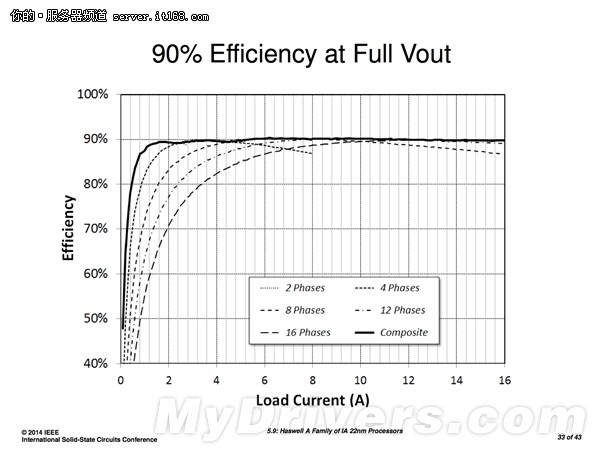

Haswell首次做到的FIVR(完全整合电压控制器)效率相当高,负载时可达90%,而且非常稳定。

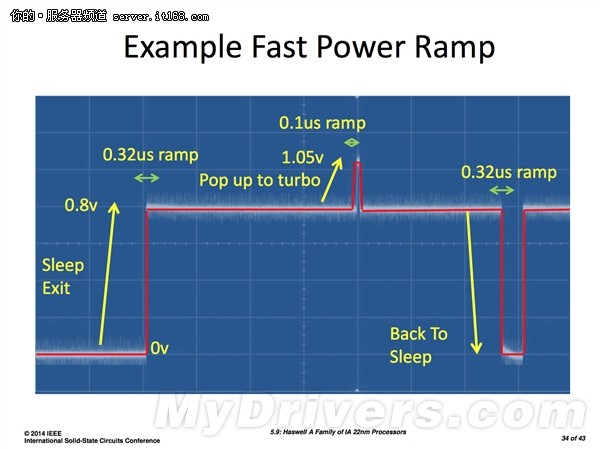

切换速度也是极快,进入/恢复睡眠只需0.32微秒,进入睿频加速更是不过0.1微秒。

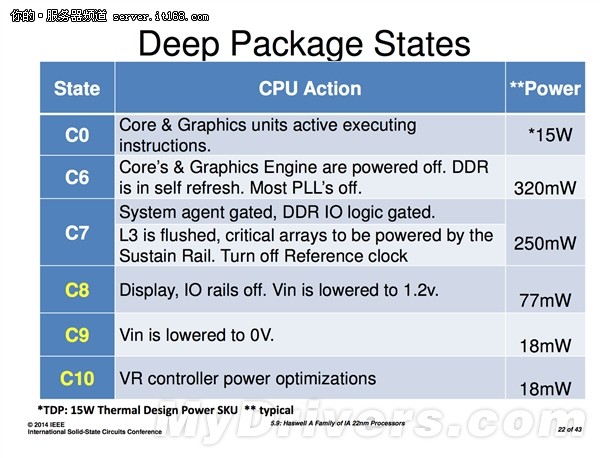

Haswell支持多种电源状态。这里以TDP 15W的超低功耗版为例,除了传统的C0、C6、C7之外,还支持三种更深度的状态:C8,关闭显示、IO部分,Vin输入电压1.2V,功耗77毫瓦;C9,Vin电压降为零,功耗18毫瓦;C10,电压控制器优化,功耗18毫瓦。